多くのエンジニアに支持されています。

PALMiCE3 SHは、ルネサス エレクトロニクス製のSuperHファミリに対応したJTAGエミュレータです。

さらなる進化を遂げたPALMiCE3

PALMiCEシリーズのコンセプトを継承して、高速化による快適なオペレーションと電源レスやコンパクト化による使いやすさを実現。 さらに、先進のマルチコア対応やCPUトレースを独自に拡張したデバッグ機能を搭載しました。

高速化を実現

より良いデバッグ機能の実現とトレースメモリの増大を考慮して、ホスト間通信の高速化を実現しました。 このことにより、トレースデータなどの内部資源の転送が高速化し、より快適なデバッグが可能となりました。

Vbus対応電源レスを継承

PALMiCEシリーズのVbus対応電源レスのコンセプトを継承して、トレースメモリを大容量化したAUDモデルでもVbus対応の電源レスを実現しました。

さらなるコンパクト設計

パフォーマンスの向上やマルチコア対応、トレースメモリの増量などの性能アップを行っても従来機種よりさらなる小型・軽量化を実現しました。

デバッグ環境の追加が低コストで可能*5

標準セットのデバッガソフト「CSIDE」とは別に同本体で使用可能なCSIDEを追加購入することで、新たなCPUのデバッグ環境が低コストで導入できます。

独自機能でAUDトレースを機能アップ*2

AUDトレースにトリガを用意してトリガの前後やトリガ間のトレースを行うトレースモードを追加したことで、問題の場所を的確にトレースすることができるようになりました。 また、分岐アドレスのサンプリング表示やCPUクロックの表示、AUDトレースのフルブレーク機能も実現しました。

先進のマルチコア対応

PALMiCE3の内部リソースをパワーアップして、より複雑なデバッグ制御を必要とするマルチコアのデバッグを可能としました。

特長

独自機能でAUDトレースを機能アップ

AUDモデルではAUDトレースの有効的な活用を考えて、下記の機能拡張をおこないました。

- AUDトレースの情報量を増大

AUDトレースの情報量を従来機種の64倍に増やしたことで、多くの分岐情報やデータアクセスを一度に取得することができます。 - 問題の場所を的確にとらえるトリガ機能*2

従来機種のAUDトレースにはなかったトリガを2点用意したことで問題の場所を的確にとらえることができます。

トリガにはプログラムアドレスやアクセスアドレス、データの指定が可能です。 - 各種トレースモードで効率的な解析*2

ブレークやトレースストップまでのトレース取得を行うフリーモードに加え、トリガ・ポイントの前後を取得するノーマルモードとスタート・トリガからエンド・トリガまでを取得するスタート/エンドモードで効率的なトレース解析が可能となりました。

CPUトレース機能*2*3

CPUトレース(CPU内蔵やAUDなど)で取得した情報を、効率的に解析して表示する機能。

トレースバック機能*2

CPUトレースの内容を解析してレジスタやメモリの値を復元し、擬似的な実行や逆ステップ実行を可能とする機能。

リアルタイム・ウォッチャー機能*2

ユーザ・プログラム実行中に影響を与えることなく、CPUメモリ空間のデータを指定周期で連続取得し、簡易グラフのリアルタイム表示やCSV型式のファイル保存が行えます。

リアルタイム・スチール機能*2*3

ユーザ・プログラムの実行中にメモリやI/Oの参照/変更が可能な機能で、リアルタイム性を必要とするターゲットのデバッグに最適です。

パフォーマンス機能*2*3

CPU内蔵の計測機能で実行時の各種サイクル数、アクセス数や実行回数等を測定してプログラムの性能測定やパフォーマンスの改善を図ることができます。

C0,C1カバレッジ機能*2

- コード・ウィンドウ上でのカバレッジ表示

- 関数単位の網羅率を表示するモジュール・カバレッジ表示

- 指定したエリアの実行領域を表示するエリア・カバレッジ表示

アンドゥ・トレース機能

トレース実行(シングルステップ実行)で行き過ぎてしまった場合に、変化したレジスタやメモリの値を擬似的に戻すことで実行結果を元に戻します。 分岐前の状態確認や値を変更しての再実行など、ちょっとした再確認が簡単に行えます。

CPUブレーク・サポート*1

CPU内蔵のブレーク・ロジックにより、プログラムの実行前ブレークやデータをリード/ライトした時のアクセス・ブレークが可能です。

シリアル・フラッシュ・メモリ対応

RZ/A1LやRZ/A1HなどのSPIマルチI/OバスコントローラやSPIインターフェースに接続されたシリアル・フラッシュ・メモリの書き込み/読み出しができます。

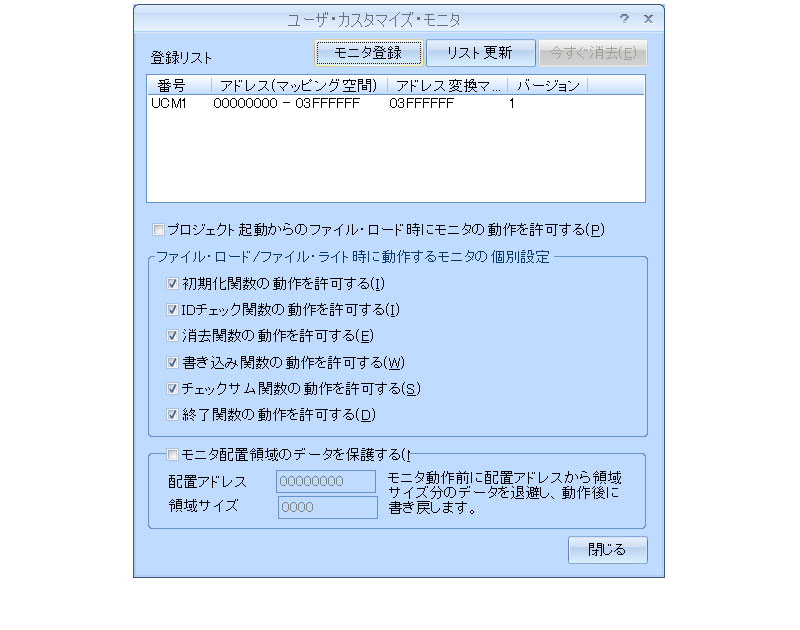

- ファイル・ロードやファイル・ライト機能で、書き込みや読み出しが可能

- 既に書き込まれているデータを残しながら、書き換えが可能

- ファイル・ロードは、バイナリ、モトローラS、ヘキサ、ELFファイル対応

- モニタ・ファイルの変更で様々なシリアル・フラッシュ・メモリに対応可能

シミュレーテッドI/O機能*2

ユーザ・プログラムの標準入出力をJTAG経由でデバッガが処理します。例えば、printf()やscanf()などのCライブラリ関数が実行された場合、デバッガのターミナル・ウィンドウで画面出力とキーボード入力が行われます。この機能はCPUをブレークさせることなくユーザ・プログラムとデバッガが通信を行う為、リアルタイム性を要求するデバッグに最適な機能となります。

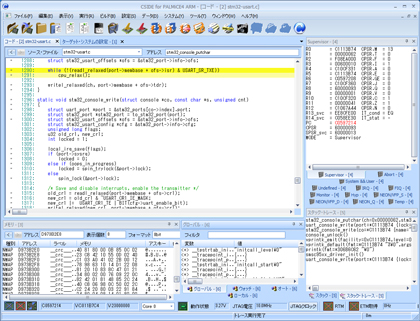

統合開発環境CSIDE Version7を標準搭載

プロジェクトの規模に関わらず、エンジニアのために本当に使いやすい統合開発環境を標準装備しています。

- バグ検出機能

- C言語と完全互換「Cマクロ」

- 簡単ソースブラウジング

- クィックインスペクトで簡単変数表示

- ラインアセンブルで命令レベルのデバッグ

- メモリ、レジスタ、コプロセッサの表示と変更

- ビットごとのI/Oの表示と変更

- スタック表示と関数スタックトレース

- フォントやウィンドウの配色が自由に設定可能

- 複数のオブジェクトファイルもワンクリックでダウンロード

- マウスジェスチャで操作可能

リアルタイムOS対応(オプション)

オプションのRTOSデバッグ・ライブラリをデバッガソフトに追加することで、 リアルタイムOSのステータス表示機能やタスクトレース機能が追加されます。(リアルタイムOSによって仕様が異なります。)

主な仕様

対応CPU

SuperHファミリ

R-CarシリーズのR-Car M1シリーズにも対応しています。

CPU個別の対応については、「サポートCPU検索」より検索していただくか、当社営業までお問い合わせください。

動作環境

| 対応ホスト | : 対応OSが動作するパソコン |

|---|---|

| ホストI/F | : USB 2.0 |

| 対応OS | : 日本語 Windows 11/10/8 (64bit /32bit) |

関連資料

- *1:CPUによって仕様が異なります。

- *2:対応CPUは、SH-4A,SH4AL-DSP,SH-2A,SH2A-FPUです。

- *3:対応CPUは、SH-2の一部です。

- *4:対応CPUは、SH-2、SH-2A、SH3-DSP、SH-4の一部です。

- *5:PALMiCE3本体モデルにより、CSIDEオプションご購入時に変換アダプタ等をあわせて購入していただく必要があります。