ハードもソフトもZynqで開発(2)2018/07/18

Zynqの回路を作ってみよう

前回はVivadoのインストールとMiniZedボードでのプロジェクトを作るところまでやりました。

今回は本格的にVivadoを使ってZynqの回路を作っていきます。ZynqはPSとPLで構成されていますが、PSだけなら割と簡単に扱うことができそうです。

Vivadoで回路を作ってみる

それでは回路を作ってみましょう。といってもそれほど気負う必要は無く、Vivadoがうまくやってくれます。今回は前回の続きで、プロジェクトを作り終えた状態からスタートします。

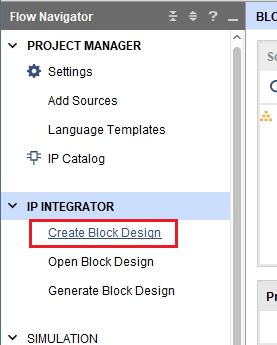

まず、ブロックデザインというのを作っていきます。これを使うとブロック図を組み合わせて回路を構成することができます。画面の左側の「Flow Navigator」から「IP INTEGRATOR」の「Create Block Design」をクリックします。

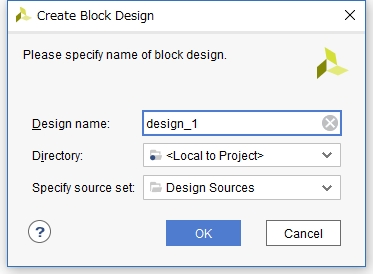

次の画面が表示されますので、デザイン名を入力します。

名前についてはVivadoがデフォルト名を用意してくれていますので、全面的にそれを受け入れることにします。ここでは「design_1」となります。

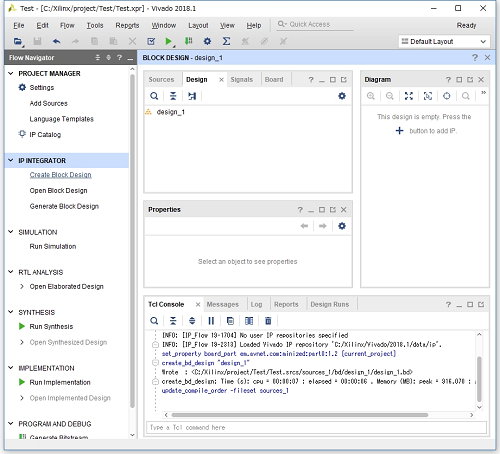

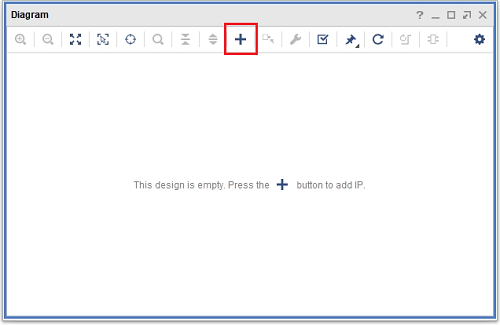

そして、OKボタンを押すと次の画面が表示されます。

Diagramのウィンドウに「+」のボタンがありますが、これをクリックすればIPを追加することができます。IPとはFPGAに搭載できる回路のモジュールのことです(微妙に違ってたらごめんなさい)。ZynqのPSとなるモジュールもここで追加し、ほかのIPと組み合わせて回路を構成していきます。

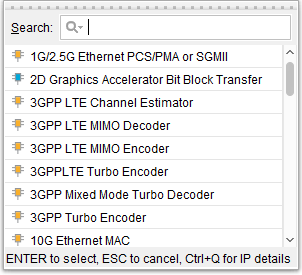

「+」ボタンを押すと、追加可能なIPがリスト表示されます。

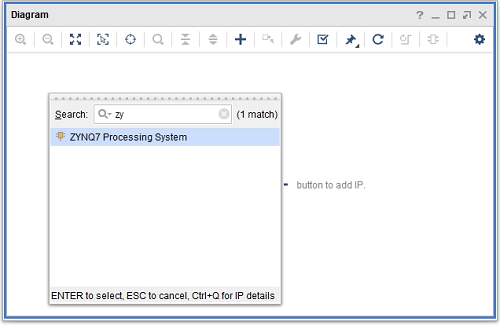

このリストから、Zynqのコアモジュールを選択します。「Search」のフィールドに文字を入力すれば、マッチするIPが表示されます。「zy」と入力すると「Zynq Processing System」がヒットします。

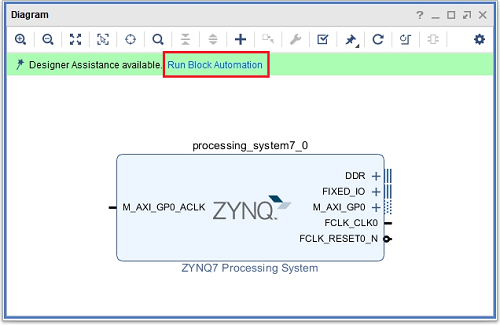

これがZynqのコアモジュールで「PS」といわれるものです。次に「Zynq Processing System」をダブルクリックすると、以下のような感じで表示されます。

ここで、秀逸なのは自動配線の機能です。IPやボードの端子へ決まったパターンで接続可能な場合は、Vivadoが自動的に配線してくれる機能があります。自動配線が可能な場合は、画面上側の緑色の帯に「Run Block Automation」が表示されますので、ここをクリックすると必要な配線が行われます。この場合は、MiniZedボードを使うための配線が行われます。

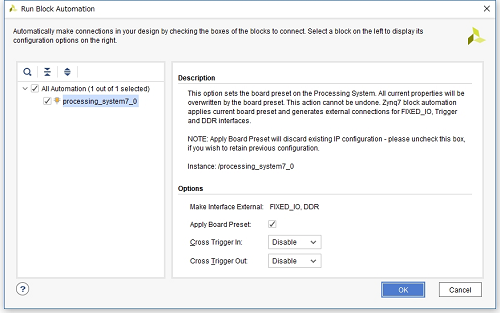

「Run Block Automation」をクリックすると、以下のようなPSの設定画面が表示されますので、デフォルトのままでOKを押します。

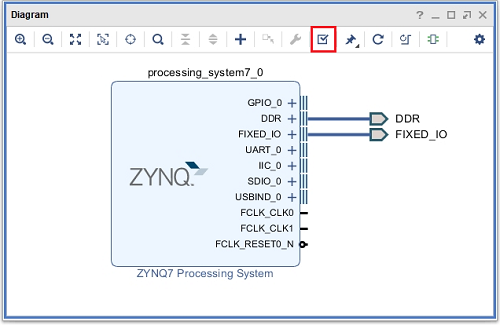

するとI/Oやクロックの出力端子が追加され、こんな形になりました。

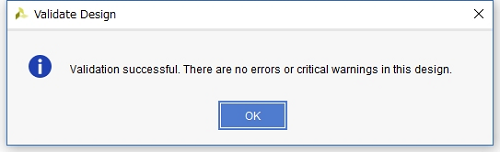

ここで上側に並んでいるボタンの「Validate Design」(チェックボックスの形のボタン)を押せば、回路の正当性をチェックしてくれます。チェックがOKなら次のメッセージが表示されます。何か問題があればエラーか警告が表示されます。

ここまでで回路的には何もない素の状態ですが、標準のGPIOは「PS LED」に接続されているはずですので、そのまま進みます。

上位層の回路を作成

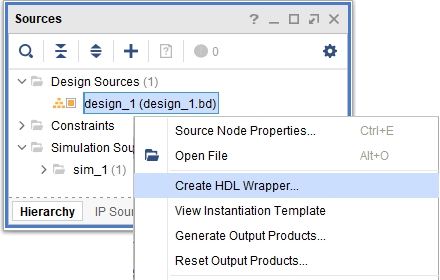

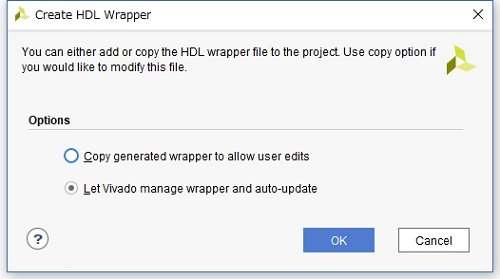

次は今作った回路に上位層を作ります。Sourcesウィンドウで「design_1(design_1.bd)」を右クリックして、メニューより「Create HDL Wrapper」を選択します。

確認のウィンドウが表示されますのでOKを押します。

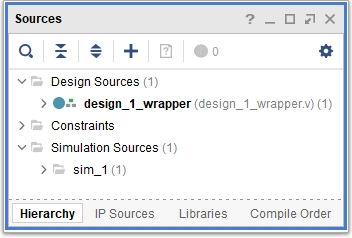

design_1_wrapperという上位層が作成されました。

上位層を作ることで回路をモジュール化し、入出力を仮想化するような目的があるのかな、と理解していますが、具体的にこれがどのように活きてくるのかはまだ謎です(すいません m(_ _)m )。

回路のコンパイルを行う

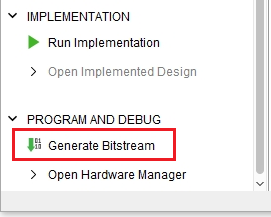

これでようやく、この回路をコンパイルする準備ができました。Flow Navigatorの「Generate Bitstream」を実行します。

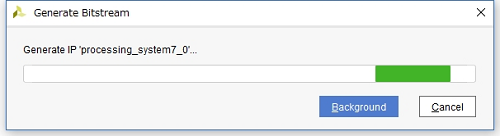

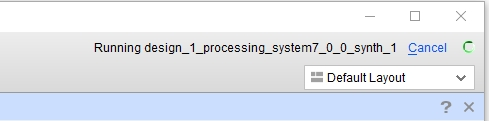

なんやかんや確認のウィンドウが表示されますが、デフォルトOKで進みます。そうしますと、何かの生成が始まります。

しばらくすると上のウィンドウが閉じますので、一瞬終わったのかと思いますが、バックグラウンドで動いています。画面の右上に進行中を示す表示がありますので注意してください。

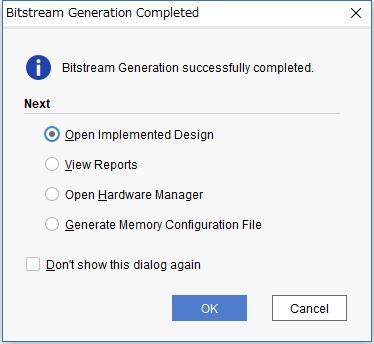

数分後、本当に処理が終わると以下のウィンドウが表示されます。

「Open Implemented Design」を開いてもいいですが、手順的には必要ないのでCancelを押してスルーします。

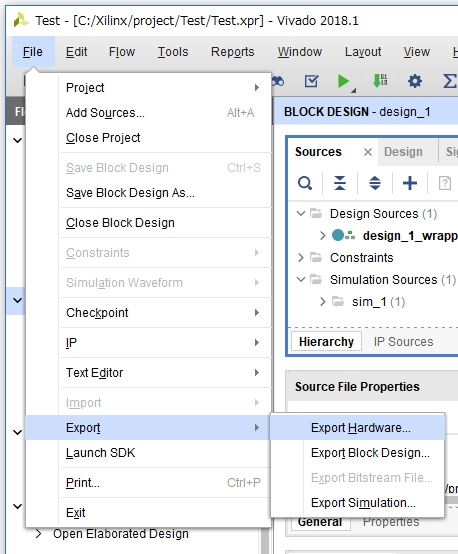

この時点で回路のコンパイルが完了しました。その成果物をソフト側に渡すために、Fileメニューの「Export」から「Export Hardware」を実行します。

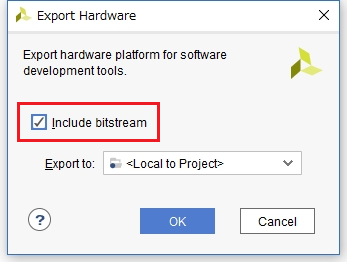

「Include bitstream」にチェックを入れてOKボタンを押します。

すると、プロジェクトのフォルダに「Test.sdk」というフォルダが作成されます。どうやらこのフォルダがSDKへ渡される情報のようです。

今回もほぼ手順説明になってしまいましたが、これでハードウェアの作業は終了です。次回はSDKを起動してLチカを実現するソフトを作ります。

Vivadoってすごい!

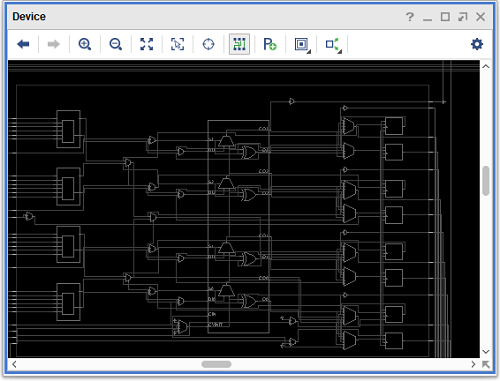

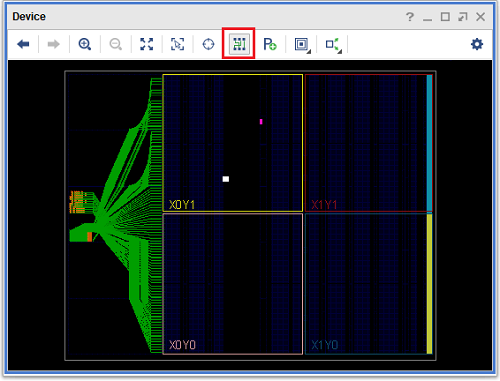

最後の手順で、Open Implemented Designをスルーしましたが、これを開くとFPGAの内部の回路が細部まで表示されます。Routing Resourcesのボタンを押すと配線が表示されます。

ズームインしていくと・・・配線が1本1本描かれています。なんかすごいです。