# On-board Flash Programmer FP-40 Technical Information

Eighth Edition (Jan. 22, 2025)

Copyright ©2023 Computex Co., Ltd.

### Table of Contents

| Document change history                                                              | 1  |

|--------------------------------------------------------------------------------------|----|

| arm Cortex series (JTAG/SWD)                                                         | 2  |

| Supported connectors                                                                 | 2  |

| Applicable products                                                                  | 2  |

| <ul> <li>FP-40 usage environment check chart</li> </ul>                              |    |

| 20-pin 2.54mm-pitch connector                                                        |    |

| ① SWD interface                                                                      |    |

| ② JTAG interface                                                                     |    |

| ■ 20-pin 1.27mm-pitch connector                                                      |    |

| (3) SWD interface                                                                    |    |

| ④ JTAG interface                                                                     |    |

| ■ 10-pin 1.27mm-pitch connector                                                      |    |

| 5 SWD interface                                                                      |    |

| 6 JTAG interface + Trace                                                             |    |

| SWD/JTAG(Cortex core)                                                                | 12 |

| <ul> <li>FP-40 target interface specifications(SWD/JTAG Cortex)</li> </ul>           |    |

| Specifications of the target connector                                               |    |

| Dimensions of TARGET cable                                                           |    |

| Target interface voltage level                                                       |    |

| Signal specifications                                                                |    |

| UART                                                                                 | 16 |

|                                                                                      |    |

| <ul> <li>Iarget interface specifications when using UART on the FP-40 unit</li></ul> |    |

| Dimensions of TARGET cable                                                           |    |

| Target interface voltage level                                                       |    |

| Signal specifications                                                                |    |

| Connection reference diagram                                                         |    |

|                                                                                      |    |

| Common specifications for each interface                                             |    |

| <ul> <li>External I/O functions of FP-40</li> </ul>                                  |    |

| External input / output function powered by VTref (1 pin)                            |    |

| External input / output function using 3.3V I/F                                      |    |

| EX_OK/EX33_OK                                                                        |    |

| EX_STARTn/EX33_STARTn                                                                |    |

| EX_BSY/EX33_BSY                                                                      |    |

| EX_NG                                                                                |    |

| Using each signal in combination                                                     |    |

| External I / O function timing with VTref (1 pin)                                    |    |

| External I / O function timing with 3.3V I/F                                         |    |

| C-Flash Settings                                                                     |    |

| Power supply                                                                         |    |

| C-Flash settings                                                                     |    |

| CPU-specific supplement                                         | .28  |

|-----------------------------------------------------------------|------|

| Reference : RZ/A and RZ/T series /SRST, /TRST reference diagram |      |

| ■ STM32C031C6T6/UART                                            | . 28 |

| Note                                                            | . 28 |

### Document change history

| First Edition   | Jul. 01, 2023 | Initial edition                                                                          |

|-----------------|---------------|------------------------------------------------------------------------------------------|

| Second Edition  | Aug. 31, 2023 | Added description of drive specs to External I/O                                         |

| Third Edition   | Feb. 05, 2024 | Added description of the TLCS-870/C1 series to UART.                                     |

|                 |               | Regarding the reference circuit diagram in ③, pins 11 and 13 have been changed to N.C.   |

| Forth Edition   | Feb. 29, 2024 | Corrected a typographical error in the description of the TLCS-870/C1 series of UARTs.   |

| Fifth Edition   | Jun. 28, 2024 | Changed the product name of the optional product "SWJ-PRB-MIL20-20HP" to                 |

|                 |               | "SWJ-PRB-MIL20-20HP-P5V".                                                                |

|                 |               | Added explanation for pins 11 and 13 in the reference circuit diagrams $(3)$ and $(4)$ . |

| Sixth Edition   | Aug. 02, 2024 | Corrected a typographical error in the description of the UART signals.                  |

| Seventh Edition | Dec. 02, 2024 | Rearrangement.                                                                           |

| Eighth Edition  | Jan. 22, 2025 | Corrected a typographical error in the description of the signal table.                  |

# arm Cortex series (JTAG/SWD)

This section describes the specifications for connecting a CPU with a core such as Cortex-M7 or Cortex-A9 to FP-40. The Cortex core has a dedicated debugging function called DAP. FP-40 uses this debugging function to control the CPU to write to flash memory. SWD or JTAG is used for communication with the DAP. SWD is an ARM proprietary. specification that extends JTAG and uses only the TMS and TCK signals of JTAG. Also, when using JTAG, the TRST signal may be required or special processing may be required to use debugging functions. Please be sure to check the CPU manual before use. This technical document describes general interface specifications.

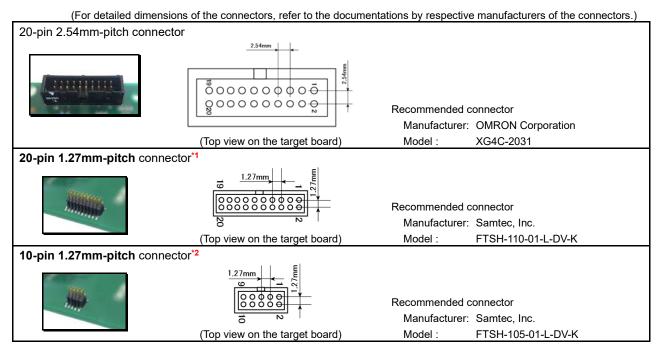

## Supported connectors

\*1: Requires a target probe "SWJ-PRB-MIL20-20HP-P5V" (Optional product).

\*2: Requires a target probe "SWJ-PRB-MIL20-10HP" (Optional product).

\* Before connecting, please refer the pin configuration diagram and make sure that the connector is in the right direction and the signals and pin numbers match. In addition to our own specifications, each company may have extended their own specifications, so be sure to check the signal names as well. The signal may be shorted and cause a malfunction.

## Applicable products

This manual is applicable for the following products:

- On-board Flash Programmer FP-40

- \* FP-40 is the upgraded model of FP-10/FP-10(model PS). The interface specifications are compatible with those of FP-10/FP-10(model PS), so existing users can replace their FP-10/FP-10(model PS) with FP-40 without modification.

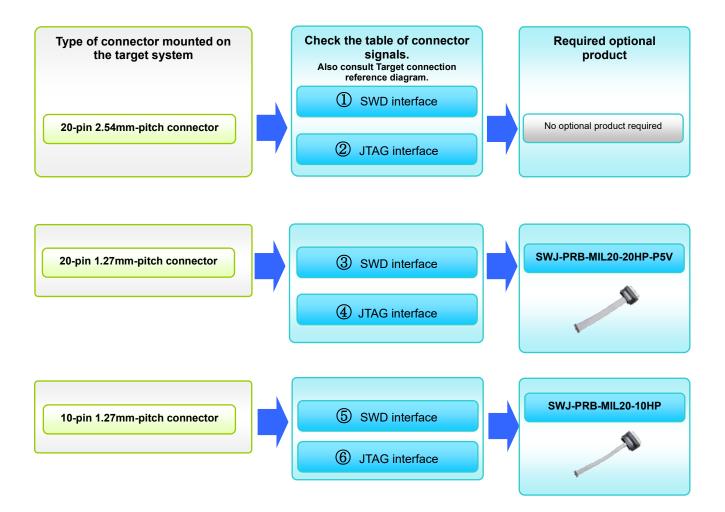

### FP-40 usage environment check chart

The following chart table summarizes the conditions required to connect a CPU employing a Cortex core to FP-40. With reference to the chart below, check to see if the current environment is suitable for FP-40 use.

\* If you are using a CPU that requires TRST, 5 and 6 cannot be used; TRST is not provided for SWJ-PRB-MIL20-10HP.

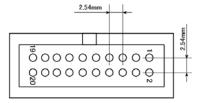

## 20-pin 2.54mm-pitch connector

#### Target connector specifications

(Top view on the target board)

Recommended connector

Manufacturer: OMRON Corporation

Model: XG4C-2031

match.

(For detailed dimensions of the connector, refer to the documentation by manufacturer of the connector.)

\*Please refer the pin configuration diagram above and make sure that the connector is in the right direction before connecting. Please check the pin number in the signal table above and make sure the signal and the pin numbers

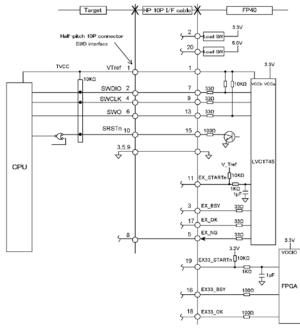

### (1) SWD interface

The SWD interface signal table when connected with a 20-pin 2.54mm pitch connector is shown below. In addition to the standard SWD signals, a power supply function and external input/output functions are supported via Connection the FP-40's unique signals.

#### Signal description

| Pin | SW     | D I/F                          | FP-4                  | 10                             | FP-40 unique   |                                                                                                                                                                                                                                                        |

|-----|--------|--------------------------------|-----------------------|--------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Signal | Input/<br>Output <sup>*1</sup> | Signal                | Input/<br>Output <sup>*1</sup> | Specifications | Connection                                                                                                                                                                                                                                             |

| 1   | VTref  | Output                         | VTref                 | Output                         | -              | Connect the I/O power supply of the CPU to be connected.                                                                                                                                                                                               |

| 2   | TVDD   | Output                         | X3.3V<br>(N.C.)       | Input                          | Yes            | TVDD signal is not used in FP-40.<br>X3.3V is a FP-40 unique signal and can be used as 3.3V<br>power supply function.<br>Please note that this signal should not be used if X5V(Pin<br>20) is used as the power supply.<br>When not used, leave as NC. |

| 3   | N.C.   | -                              | EX_BSY<br>(N.C.)      | Input                          | Yes            | EX_BSY is a FP-40 unique signal and outputs the operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                            |

| 4   | GND    | -                              | GND                   | -                              | -              |                                                                                                                                                                                                                                                        |

| 5   | N.C.   | -                              | EX_NG<br>(N.C.)       | Input                          | Yes            | EX_NG is an FP-40 original signal and outputs the operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                          |

| 6   | GND    | -                              | GND                   | -                              | -              |                                                                                                                                                                                                                                                        |

| 7   | SWDIO  | Input/Output                   | SWDIO                 | Input/Output                   | -              |                                                                                                                                                                                                                                                        |

| 8   | GND    | -                              | GND                   | -                              | -              |                                                                                                                                                                                                                                                        |

| 9   | SWCLK  | Input                          | SWCLK                 | Input                          | -              |                                                                                                                                                                                                                                                        |

| 10  | GND    | -                              | GND                   | -                              | -              |                                                                                                                                                                                                                                                        |

| 11  | N.C.   | -                              | EX_STARTn<br>(N.C.)   | Output                         | Yes            | EX_STARTn is a FP-40 unique signal and can be used as a<br>write start request signal to FP-40.<br>When not used, leave as NC.                                                                                                                         |

| 12  | GND    | -                              | GND                   | -                              | -              |                                                                                                                                                                                                                                                        |

| 13  | SWO    | Output                         | N.C.                  | -                              | Yes            | NC as this signal is not used.                                                                                                                                                                                                                         |

| 14  | GND    | -                              | GND                   | -                              | -              |                                                                                                                                                                                                                                                        |

| 15  | SRSTn  | Input                          | SRSTn                 | Input                          | -              | Connect the reset signal to the connected CPU with a wired<br>OR circuit or an OR circuit. The SRSTn signal is an open<br>collector output.                                                                                                            |

| 16  | GND    | -                              | EX33_BSY<br>(N.C.)    | Input                          | Yes            | EX33_BSY is an FP-40 original signal and outputs the<br>operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                    |

| 17  | N.C.   | -                              | EX_OK<br>(N.C.)       | Input                          | Yes            | EX_OK is an FP-40 original signal and outputs the operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                          |

| 18  | GND    | -                              | EX33_OK<br>(N.C.)     | Input                          | Yes            | EX33_OK is an FP-40 original signal and outputs the<br>operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                     |

| 19  | N.C.   | -                              | EX33_STARTn<br>(N.C.) | Output                         | Yes            | EX33_STARTn is an FP-40 original signal and can be used<br>as a write start request signal to FP-40.<br>When not used, leave as NC.                                                                                                                    |

| 20  | GND    | -                              | X5V<br>(N.C.)         | Input                          | Yes            | X5V is FP-40's unique signal and can be used as 5V power<br>supply function.<br>Cannot be used with 2-pin 3.3V power supply. If not used,<br>leave as NC.<br>Do not use as a power supply function when connected to<br>GND.                           |

\*1: Input/output is based on the target system.

#### Signal table

| Pin<br>No. | Signal                        | Input/<br>Output<br>*1 | Pin<br>No. | Signal                  | Input/<br>Output<br>*1 |

|------------|-------------------------------|------------------------|------------|-------------------------|------------------------|

| 1          | VTref                         | Output                 | 2          | [X3.3V] *5              | Input                  |

| 3          | (EX_BSY)*2                    | Input                  | 4          | GND                     |                        |

| 5          | (EX_NG)*2                     | Input                  | 6          | GND                     |                        |

| 7          | SWDIO                         | Input/<br>Output       | 8          | GND                     |                        |

| 9          | SWCLK                         | Input                  | 10         | GND                     |                        |

| 11         | (EX_STARTn)*2                 | Output                 | 12         | GND                     |                        |

| 13         | SWO*3                         | Output                 | 14         | GND                     |                        |

| 15         | SRSTn                         | Input                  | 16         | <ex33_bsy>*4</ex33_bsy> | Input                  |

| 17         | (EX_OK)*2                     | Input                  | 18         | <ex33_ok>*4</ex33_ok>   | Input                  |

| 19         | <ex33_startn>*4</ex33_startn> | Output                 | 20         | [X5V] *5                | Input                  |

Input/output is denoted for the target system. \*1:

\*2: External input/output function signal that will be at VTref level when high.

This signal is not connected to the target (CPU).

\*3: Unused. NC. \*4: 3.3V Externa \*4: 3.3V External input/output function signal. This signal is not connected to the target (CPU).

\*5: Power supply function signal.

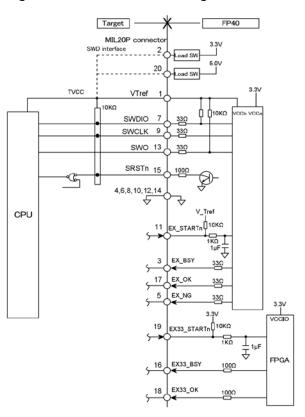

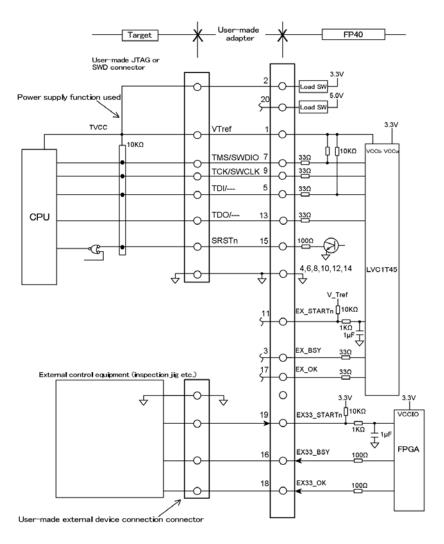

#### Target connection reference diagram

To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible. If the waveform disturbance exceeds the device specifications, suppress the disturbance by inserting a damping resistor into the signal line or use other means.

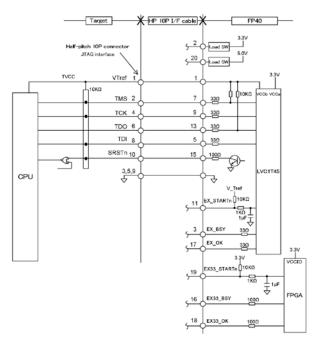

## 2 JTAG interface

The JTAG interface signal table when connected with a 20-pin 2.54mm pitch connector is shown below. In addition to the standard JTAG signal, FP-40 provides power supply function and external input/output function by FP-40's original signal.

#### Signal description

| Pin | JTAG I/                 | F                              | FP-40                     | )                              | FP-40 unique   |                                                                                                                                                                                                                                                        |

|-----|-------------------------|--------------------------------|---------------------------|--------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Signal                  | Input/<br>Output <sup>*1</sup> | Signal                    | Input/<br>Output <sup>*1</sup> | Specifications | Connection                                                                                                                                                                                                                                             |

| 1   | VTref                   | Output                         | VTref                     | Output                         | -              | Connect the I/O power supply of the CPU to be connected.                                                                                                                                                                                               |

| 2   | TVDD                    | Output                         | X3.3V<br>(N.C.)           | Input                          | Yes            | TVDD signal is not used in FP-40.<br>X3.3V is a FP-40 unique signal and can be used as 3.3V<br>power supply function.<br>Please note that this signal should not be used if X5V(Pin<br>20) is used as the power supply.<br>When not used, leave as NC. |

| 3   | TRST/<br>N.C.(Cortex-M) | -                              | TRST                      | Input                          | -              | TRST is not used with Cortex-M core CPUs. Leave as NC.<br>For CPUs other than Cortex-M, please refer to the<br>datasheet.                                                                                                                              |

| 4   | GND                     | -                              | GND                       | -                              | -              |                                                                                                                                                                                                                                                        |

| 5   | TDI                     | Input                          | TDI                       | Input                          | -              |                                                                                                                                                                                                                                                        |

| 6   | GND                     | -                              | GND                       | -                              | -              |                                                                                                                                                                                                                                                        |

| 7   | TMS                     | Input                          | TMS                       | Input                          | -              |                                                                                                                                                                                                                                                        |

| 8   | GND                     | -                              | GND                       | -                              | -              |                                                                                                                                                                                                                                                        |

| 9   | TCK                     | Input                          | TCK                       | Input                          | -              |                                                                                                                                                                                                                                                        |

| 10  | GND                     | -                              | GND                       | -                              | -              |                                                                                                                                                                                                                                                        |

| 11  | N.C.                    | -                              | N.C.                      | -                              | -              |                                                                                                                                                                                                                                                        |

| 12  | GND                     | -                              | GND                       | -                              | -              |                                                                                                                                                                                                                                                        |

| 13  | TDO                     | Output                         | TDO                       | Output                         | -              |                                                                                                                                                                                                                                                        |

| 14  | GND                     | -                              | GND                       | -                              | -              |                                                                                                                                                                                                                                                        |

| 15  | SRSTn                   | Input                          | SRSTn                     | Input                          | -              | Connect the reset signal to the connected CPU with a<br>wired OR circuit or an OR circuit. The SRSTn signal is an<br>open collector output.                                                                                                            |

| 16  | GND                     | -                              | EX33_BSY<br>(N.C.)        | Input                          | Yes            | EX33_BSY is an FP-40 original signal and outputs the<br>operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                    |

| 17  | N.C.                    | -                              | N.C.                      | -                              | -              |                                                                                                                                                                                                                                                        |

| 18  | GND                     | -                              | EX33_OK<br>(N.C.)         | Input                          | Yes            | EX33_OK is an FP-40 original signal and outputs the<br>operation status from FP-40.<br>When not used, leave as NC.                                                                                                                                     |

| 19  | N.C.                    | -                              | EX33_START<br>n<br>(N.C.) | Output                         | Yes            | EX33_STARTn is an FP-40 original signal and can be<br>used as a write start request signal to FP-40.<br>When not used, leave as NC.                                                                                                                    |

| 20  | GND                     | -                              | X5V<br>(N.C.)             | Input                          | Yes            | X5V is FP-40's unique signal and can be used as 5V<br>power supply function.<br>Cannot be used with 2-pin 3.3V power supply. If not used,<br>leave as NC.<br>Do not use as a power supply function when connected to<br>GND.                           |

**\*1**: Input/output is based on the target system.

#### Signal table

#### Input/ Input/ Pin Pin Output Output Signal Signal No. No. VTref Output 2 [X3.3V] Input 1 TRST (N.C.)\* 4 3 GND Input 5 7 TDI Input 6 GND TMS Input 8 GND 9 TCK Input 10 GND 11 Output GND N.C.\* 12 13 TDO Output 14 GND 15 SRSTn Input 16 <EX33\_BSY>\*3 Input 17 18 N.C. Input <EX33\_OK> Input 19 <EX33\_STARTn>\*3 Output 20 [X5V] Input

\*1: Input/output denoted is for the target system.

\*2: TRST TRST is not used with Cortex-M core CPUs. Leave as NC. For other CPUs, please refer to the datasheet of the CPU to be connected. Please note that CPUs that require connection may require the signals to be pulled-down.

Note that some CPUs manufactured by Renesas Electronics require some precautions. Refer to "Reference:RZ/A and RZ/T series /SRST, /TRST reference diagram" below.

\*3: 3.3V External input/output function signal. This signal is not connected to the target (CPU).

\*4: Power supply function signal.

\*5: Reserved for FP-40's own usage, leave as NC.

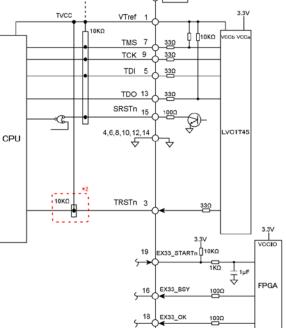

#### FP40 Target MIL20P co 3.3V JTAC terface 2 5.0V 20 тисс VTret , 10KΩ

Target connection reference diagram

To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible.

If the waveform disturbance exceeds the device specifications, suppress the disturbance by inserting a damping resistor into the signal line or use other means.

### 20-pin 1.27mm-pitch connector

#### Target connector specifications

(Top view on the target board)

Recommended connector

Manufacturer: Samtec, Inc.

Model: FTSH-110-01-L-DV-K

(For detailed dimensions of the connector, refer to the documentation by manufacturer of the connector.)

\*Please refer the pin configuration diagram above and make sure that the connector is in the right direction before connecting.

Please check the pin number in the signal table above and make sure the signal and the pin numbers match.

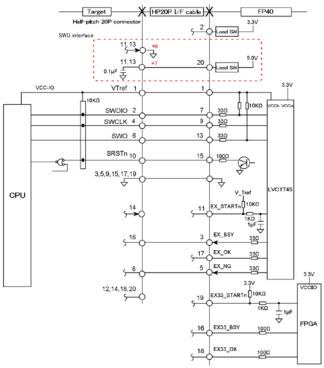

#### (3) SWD interface

The signal table and target connection reference diagram when connecting a 20-pin 1.27mm pitch connector with SWD interface are shown below.

#### Signal table

| Pin<br>No. | Signal              | Input/<br>Output<br>*1 | Pin<br>No. | Signal              | Input/<br>Output<br>*1 |

|------------|---------------------|------------------------|------------|---------------------|------------------------|

| 1          | VTref <sup>*2</sup> | Output                 | 2          | SWDIO               | Input/<br>Output       |

| 3          | GND                 |                        | 4          | SWCLK               | Input                  |

| 5          | GND                 |                        | 6          | SWO*3               | Output                 |

| 7          | Key*5               |                        | 8          | NC                  | NC                     |

| 9          | GND                 |                        | 10         | SRSTn <sup>*4</sup> | Input                  |

| 11         | GND*6/TgtPwr*7      |                        | 12         | TraceClk*3          | Output                 |

| 13         | GND*6/TgtPwr*7      |                        | 14         | TraceD0*3           | Output                 |

| 15         | GND                 |                        | 16         | TraceD1*3           | Output                 |

| 17         | GND                 |                        | 18         | TraceD2*3           | Output                 |

| 19         | GND                 |                        | 20         | TraceD3*3           | Output                 |

\*1: Input/output is denoted for the target system.\*2: Connect the I/O power supply of the CPU to VTref.

\*3: Unused. NC.

\*4: Connect the reset signal to the connected CPU with a wired OR circuit or an OR circuit. The SRSTn signal is an open collector output.

- **\*5**: Intended for protection against erroneous insertion.

- \*6: If SWJ-PRB-MIL20-20HP is used, this can be left as NC

\*7: If SWJ-PRB-MIL20-20HP-P5V is used, the power supply function of FP can be used. If the power supply function is not used, leave the pins as NC.

#### Target connection reference diagram

To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible.

If the waveform disturbance exceeds the device specifications, suppress the disturbance by inserting a damping resistor into the signal line or use other means.

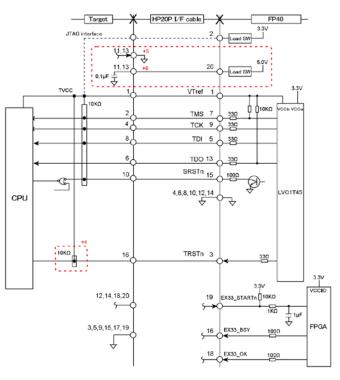

### **4** JTAG interface

The signal table and target connection reference diagram when connecting a 20-pin 1.27mm pitch connector with JTAG interface are shown below.

#### Signal table

| Pin<br>No. | Signal         | Input/<br>Output<br>*1 | Pin<br>No. | Signal | Input/<br>Output<br>*1 |

|------------|----------------|------------------------|------------|--------|------------------------|

| 1          | VTref          | Output                 | 2          | TMS    | Input                  |

| 3          | GND            |                        | 4          | TCK    | Input                  |

| 5          | GND            |                        | 6          | TDO    | Output                 |

| 7          | Key*3          |                        | 8          | TDI    | Input                  |

| 9          | GND            |                        | 10         | SRST*2 | Input                  |

| 11         | GND*5/TgtPwr*6 |                        | 12         | NC     |                        |

| 13         | GND*5/TgtPwr*6 |                        | 14         | NC     | Output                 |

| 15         | GND            |                        | 16         | TRST*4 | Input                  |

| 17         | GND            |                        | 18         | NC     |                        |

| 19         | GND            |                        | 20         | NC     |                        |

\*1: Input/output is denoted for the target system.

\*2: SRST is an open drain output signal. Connect to the target system's "power-on reset" or "system reset" with a wired OR circuit or, if a wired OR circuit is not possible, with an OR circuit. VCC should be connected to a power supply matching the circuitry of the target system at 5 V or less.

\*3: Intended for protection against erroneous insertion.

- \*4: TRST is not used with Cortex-M core CPUs. Leave as NC. For other CPUs, please refer to the datasheet of the CPU to be connected.

- Please note that CPUs that require connection may require the signals to be pulled-down.

Note that some CPUs manufactured by Renesas Electronics require some precautions. Refer to "Reference : RZ/A and RZ/T series /SRST, /TRST reference diagram " below.

\*5: If SWJ-PRB-MIL20-20HP is used, this can be left as NC

6: If SWJ-PRB-MIL20-20HP-P5V is used, the power supply function of FP can be used. If the power supply function is not used, leave the pins as NC.

#### Target connection reference diagram

To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible.

### 10-pin 1.27mm-pitch connector

#### Target connector specifications

(Top view on the target board)

Recommended connector Manufacturer:Samtec, Inc. Model: FTSH-105-01-L-DV-K (For detailed dimensions of the connector, refer to the documentation by manufacturer of the connector.)

\*Please refer the pin configuration diagram above and make sure that the connector is in the right direction before connecting.

Please check the pin number in the signal table above and make sure the signal and the pin numbers match.

This connector does not support the power supply function to the target.

### **(5)** SWD interface

The signal table and target connection reference diagram when connecting a 10-pin 1.27mm pitch connector with SWD interface are shown below.

#### Signal table

| Pin<br>No. | Signal  | Input/<br>Output *1 | Pin<br>No. | Signal              | Input/<br>Output *1 |

|------------|---------|---------------------|------------|---------------------|---------------------|

| 1          | VTref*2 | Output              | 2          | SWDIO               | Input/<br>Output    |

| 3          | GND     |                     | 4          | SWCLK               | Input               |

| 5          | GND     |                     | 6          | SWO*3               | Output              |

| 7          | Key*5   |                     | 8          | NC                  | Input               |

| 9          | GND     |                     | 10         | SRSTn <sup>*4</sup> | Input               |

\*1: Input/output is denoted for the target system.\*2: Connect the I/O power supply of the CPU to VTref.

\*3: Unused. NC.

- \*4: Connect the reset signal to the connected CPU with a wired OR circuit or an OR circuit. The SRSTn signal is an open collector output.

- **\*5**: Intended for protection against erroneous insertion.

#### Target connection reference diagram

To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible.

If the waveform disturbance exceeds the device specifications, suppress the disturbance by inserting a damping resistor into the signal line or use other means.

### **6** JTAG interface + Trace

The signal table and target connection reference diagram when connecting a 10-pin 1.27mm pitch connector with JTAG interface are shown below.

#### Signal table

| Pin<br>No. | Signal | Input/<br>Output *1 | Pin<br>No. | Signal  | Input/<br>Output <sup>*1</sup> |

|------------|--------|---------------------|------------|---------|--------------------------------|

| 1          | Vtref  | Output              | 2          | TMS     | Input                          |

| 3          | GND    |                     | 4          | TCK     | Input                          |

| 5          | GND    |                     | 6          | TDO     | Output                         |

| 7          | Key*3  |                     | 8          | TDI     | Input                          |

| 9          | GND    |                     | 10         | SRSTn*2 | Input                          |

\*1: Input/output is denoted for the target system.

\*2: Connect the reset signal to the connected CPU with a wired OR circuit or an OR circuit. The SRSTn signal is an open collector output.

\*3: Intended for protection against erroneous insertion.

#### Target connection reference diagram

To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible.

If the waveform disturbance exceeds the device specifications, suppress the disturbance by inserting a damping resistor into the signal line or use other means.

# SWD/JTAG(Cortex core)

Refer to the interface specifications below to connect to the target.

### FP-40 target interface specifications(SWD/JTAG Cortex)

This chapter describes the target interface specifications for connecting FP-40 to the target.

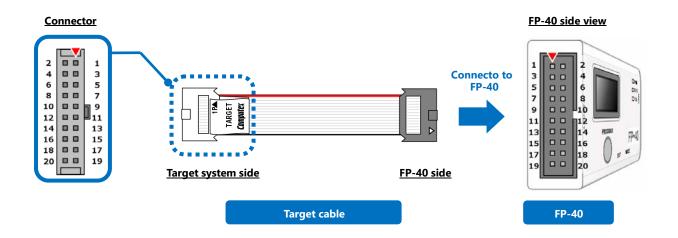

#### Specifications of the target connector

The standard interfaces supported by FP-40 are JTAG and SWD, and the connector specification is MIL 20-pin with 2.54mm pitch. Connection to the target system is made using the supplied dedicated interface cable (TARGET cable). For interfaces other than JTAG and SWD, please refer to their individual instruction manuals.

Pin allocation

The pin allocations are specific to FP-40 and the target cable is dedicated to FP-40. <u>Make sure that you only use</u> the TARGET cable that is included with the product.

|     |                 | la mati                        |                                            |                | access point         |              |  |  |

|-----|-----------------|--------------------------------|--------------------------------------------|----------------|----------------------|--------------|--|--|

| No. | Signal *1       | Input/<br>Output <sup>*2</sup> | FP-40 internal circuit                     | 20-pin         | 20-pin               | 10-pin       |  |  |

|     |                 | -                              |                                            | 2.54mm-pitch   | 1.27mm-pitch         | 1.27mm-pitch |  |  |

| 1   | VTref           | Output                         | 4KΩPull-Down                               | 1              | 1                    | 1            |  |  |

| 2   | X3.3V           | Input                          | Power supply<br>(when output is permitted) | 2              | -                    | -            |  |  |

| 3   | TRST / (EX_BSY) | Input                          | 22Ωseries                                  | 3              | 16                   | -            |  |  |

| 4   | GND             |                                | GND                                        | 4,6,8,10,12,14 | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 5   | TDI / (EX_NG)   | Input                          | 22Ωseries                                  | 5              | 8                    | 8            |  |  |

| 6   | GND             |                                | GND                                        | 4,6,8,10,12,14 | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 7   | TMS/SWDIO       | Input /<br>Input/Output        | 22Ωseries<br>10KΩPull-Up (VTref)           | 7              | 2                    | 2            |  |  |

| 8   | GND             |                                | GND                                        | 4,6,8,10,12,14 | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 9   | TCK/SWCLK       | Input                          | 22Ωseries                                  | 9              | 4                    | 4            |  |  |

| 10  | GND             |                                | GND                                        | 4,6,8,10,12,14 | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 11  | (EX_STARTn)     | Output                         | 1KΩseries<br>10KΩPull-Up (VTref)           | 11             | -                    | -            |  |  |

| 12  | GND             |                                | GND                                        | 4,6,8,10,12,14 | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 13  | TDO/SWO         | Output                         | 22Ωseries<br>10KΩPull-Up (VTref)           | 13             | 6                    | 6            |  |  |

| 14  | GND             |                                | GND                                        | 4,6,8,10,12,14 | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 15  | SRSTn           | Input                          | 100Ωseries<br>Open-collector output        | 15             | 10                   | 10           |  |  |

| 16  | (EX33_BSY)      | Input                          | 100Ωseries                                 | 16             | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 17  | (EX_OK)         | Input                          | 22Ωseries                                  | 17             | -                    | -            |  |  |

| 18  | (EX33_OK)       | Input                          | 100Ωseries                                 | 18             | 3,5,9,11,13,15,17,19 | 3,5,9        |  |  |

| 19  | (EX33_STARTn)   | Output                         | 1KΩseries<br>10KΩPull-Up (3.3V)            | 19             | -                    | -            |  |  |

| 20  | (X5V)           | Input                          | Power supply<br>(when output is permitted) | 20             | -                    | -            |  |  |

\*1 : Signal names in parentheses () are signals with FP-40's unique specifications. \*2 : Input/Output is based on the target system.

#### **Dimensions of TARGET cable**

Dimensions of the dedicated TARGET cable are as follows.

#### Target interface voltage level

Input voltage level

| Target voltage (V) | 5.0V | 3.3V | 1.8V  |

|--------------------|------|------|-------|

| VIH(min)           | 3.5V | 2.0V | 1.17V |

| VIL(max)           | 1.5V | 0.8V | 0.63V |

Output voltage level

| Target voltage (V) | 4.5V  | 3.0V  | 1.65V |  |  |

|--------------------|-------|-------|-------|--|--|

| VOH(min)           | 3.8V  | 2.4V  | 1.2V  |  |  |

| VOL(max)           | 0.55V | 0.55V | 0.45V |  |  |

#### Signal specifications

JTAG/SWD signals (TCK, TMS, TDI, TDO, SWDIO and SWCLK)

FP-40 communicates with the on-chip debug unit in the ARM core via the JTAG or SWD connections. JTAG uses four signal lines - TCK, TMS, TDI and TDO, while SWD required two - SWDIO and SWCLK. The signal designation may differ slightly depending on the CPU, but generally for CPUs that use both JTAG and SWD, TMS and SWDIO, TCK and SWCLK use the same terminals.

Make sure to check the specifications of the target CPU before connecting the necessary signals. Please note that  $\overline{\text{TRST}}$  (reset signal for JTAG) is not used.

#### SRST signal

SRST signal is used as the reset signal for initializing the CPU from FP-40.

The output from FP-40 is open-collector to allow wired-OR connections on the power-on-reset and system reset signals on the target.

Please refer to the CPU datasheet, etc., as the CPU may have its own extensions. Please be especially careful with Renesas CPUs.

#### TRST signal

Reset signal to initialize the CPU JTAG from FP-40.

If SWD is used, there is no need to connect this signal. Also, with Cortex-M core CPUs, even if you are using JTAG, you do not need to connect  $\overline{\text{TRST}}$ .

Please refer to the CPU datasheet, etc., for  $\overline{\text{TRST}}$  connections, as they may have been uniquely extended by the CPU. Please be especially careful with Renesas CPUs. The output from the FP-40 is an open collector output to allow wired OR with the target system's power-on reset or system reset signal.

Since the  $\overline{\text{TRST}}$  signals of SWJ-PRB-MIL20-10HP and FP-40 are not connected, it is necessary to make your own cable for "10-pin connector 1.27mm pitch" connection on CPUs that require  $\overline{\text{TRST}}$ .

#### VTref signal

Connect the CPU's I/O power to this signal. The valid range should be 1.65V~5.5V. FP-40 communicates at a signal level that follows the potential connected to this signal. However, some of FP-40 unique signals are 3.3V dedicated I/F. For specifications, refer to "External I/O functions of FP-40".

#### X3.3V/X5V power supply

This can be used as the power supply from FP-40 to the target system. The two pins of the target connector are X3.3V (3.3V) and the 20 pins are X5V (5V), both of which guarantee ±5% accuracy and can supply up to 200mA. The rise time upon power-on is 2ms. 3.3V or 5V can be used depending on the C-Flash setting, but they can't be used simultaneously. For details on the settings, refer to "**4.3 Target Settings**" in "**Onboard Flash Memory Programmer FP User's Manual**". These power supplies are equipped with a protection circuit that cuts the power supply if an overcurrent is detected due to a short circuit on the target. To confirm that power is normally supplied to the target, the voltage of VTref is measured by software processing after power is supplied, and if the voltage of VTref is lower than the [minimum input voltage of VTref (Pin 1)], the power output is stopped to protect FP-40 itself.

If these pins are not used, leave them as NC.

#### External I/O function signals

These signals are for the FP-40's external I/O functions. EX\_BSY, EX\_NG, EX\_STARTn, EX\_OK, EX33\_BSY, EX33\_OK, and EX33\_STARTn are assigned to the target connector respectively. The target connector signals are normally connected to the target system in which the CPU to be written is mounted, but these signals are intended to be connected to an external production system or other controller device that controls FP-40. Please refer to "External I/O functions of FP-40" for detailed specifications.

If the External I/O functions of FP-40 is not used, leave these signals as NC.

The specifications are the same as those of the conventional FP-10 model.

# UART

A dedicated cable is not provided to use UART. Refer to the interface specifications below to connect to the target.

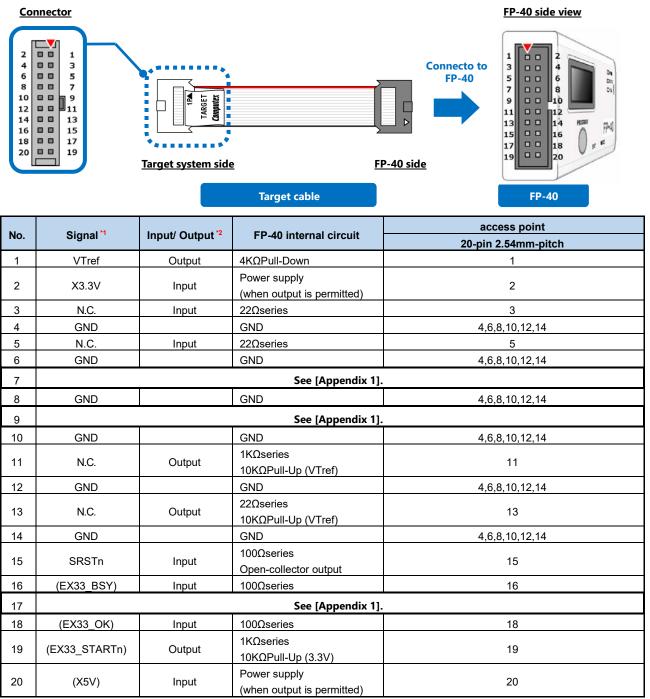

### Target interface specifications when using UART on the FP-40 unit

This section describes the interface specifications on the FP-40 unit for connecting the FP-40 to a UART on the target on the.

#### Specifications of the target connector

Pin allocation

\*1 : Signal names in parentheses () are signals with FP-40's unique specifications.

\*2 : Input/Output is based on the target system.

#### [Appendix 1]

|     |                | MD termin        | al is used     |                  | MD terminal not used |                  |                |                  | FP-40 internal                   | access<br>point  |

|-----|----------------|------------------|----------------|------------------|----------------------|------------------|----------------|------------------|----------------------------------|------------------|

| No. | Targe          | t side           | FP side        |                  | Target side          |                  | FP side        |                  | circuit                          | 20-pin           |

|     | signal<br>name | Input/<br>Output | signal<br>name | Input/<br>Output | signal<br>name       | Input/<br>Output | signal<br>name | Input/<br>Output |                                  | 2.54mm<br>-pitch |

| 7   | TXD            | Output           | RXD            | Input            | RXD                  | Input            | TXD            | Output           | 22Ωseries<br>10KΩPull-Up (vTref) | 7                |

| 9   | RXD            | Input            | TXD            | Output           | TXD                  | Output           | RXD            | Input            | 22Ωseries                        | 9                |

| 17  | MODE           | Input            | MODE           | Output           | N.C.                 |                  |                |                  | 22Ωseries                        | 17               |

#### **Dimensions of TARGET cable**

Dimensions of the dedicated TARGET cable are as follows.

#### Target interface voltage level

#### Input voltage level

| Target voltage | ge (V) | 5.0V | 3.3V | 1.8V  |  |  |

|----------------|--------|------|------|-------|--|--|

| VIH(min        | )      | 3.5V | 2.0V | 1.17V |  |  |

| VIL(max        | .)     | 1.5V | 0.8V | 0.63V |  |  |

#### Output voltage level

| Target voltage (V) | 4.5V  | 3.0V  | 1.65V |

|--------------------|-------|-------|-------|

| VOH(min)           | 3.8V  | 2.4V  | 1.2V  |

| VOL(max)           | 0.55V | 0.55V | 0.45V |

#### Signal specifications

**RXD/TXD** signals

UART RXD/TXD signals.

#### SRST signal

SRST signal is used as the reset signal for initializing the CPU from FP-40. The output from FP-40 is open-collector to allow wired-OR connections on the power-on-reset and system reset signals on the target.

#### VTref signal

Connect the CPU's I/O power to this signal. The valid range should be 1.65V~5.5V. FP-40 communicates at a signal level that follows the potential connected to this signal. However, some of FP-40 unique signals are 3.3V dedicated I/F. For specifications, refer to "External I/O functions of FP-40".

#### MODE signal

Connect the signal that needs to be controlled when switching CPU boot mode, such as TLCS-870/C1 or RX210. The name of this signal varies depending on the CPU, such as MODE pin or MD pin. If the CPU is not used, it is N.C.

#### X3.3V/X5V power supply

This can be used as the power supply from FP-40 to the target system. The two pins of the target connector are X3.3V (3.3V) and the 20 pins are X5V (5V), both of which guarantee ±5% accuracy and can supply up to 200mA. The rise time upon power-on is 2ms. 3.3V or 5V can be used depending on the C-Flash setting, but they can't be used simultaneously. For details on the settings, refer to **"4.3 Target Settings"** in **"Onboard Flash Memory Programmer FP User's Manual**". These power supplies are equipped with a protection circuit that cuts the power supply if an overcurrent is detected due to a short circuit on the target. To confirm that power is normally supplied to the target, the voltage of VTref is measured by software processing after power is supplied, and if the voltage of VTref is lower than the **[minimum input voltage of VTref (Pin 1)]**, the power output is stopped to protect FP-40 itself. If these pins are not used, leave them as NC.

External I/O function signals of FP-40

Please refer to "External I/O functions of FP-40" for detailed specifications.

If the External I/O functions of FP-40 is not used, leave these signals as NC.

Note that when using UART, external input/output functions (EX\_OK, EX\_NG, EX\_STARTn, EX\_BSY) that are powered by VTref (1pin) cannot be used.

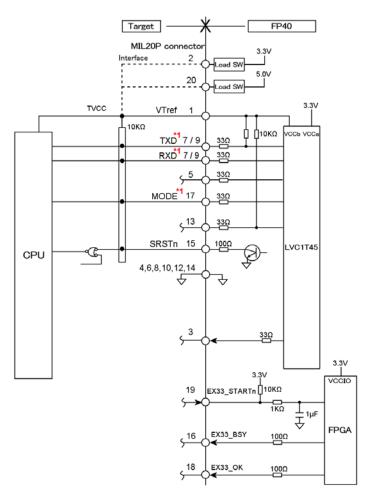

#### Connection reference diagram

\*1: By CPU.

# **Common specifications for each interface**

This is a specification of functions that can be used commonly in each interface.

### External I/O functions of FP-40

The following signals are provided to allow FP-40 to be operated by an external controller. For information about the Target connector, refer to section "Specifications of the target connector".

#### External input / output function powered by VTref (1 pin)

This function is available only for SWD interface. It is not available for other interfaces.

| Pin No. | Signal                  | Description                                           | Command    |

|---------|-------------------------|-------------------------------------------------------|------------|

| 3       | EX_BSY*1                | Outputs high from FP-40 during writing                | FP_EXBSY   |

| 5       | EX_NG <sup>*1</sup>     | If the write result is NG, high is output from FP-40. | FP_EXNG    |

| 11      | EX_STARTn <sup>*2</sup> | Start writing when there is a pulse input to FP-40    | FP_EXSTART |

| 17      | EX_OK*1                 | When the write result is OK, H is output from FP      | FP_EXOK    |

\*1: Hi level will be the same as the VTref (Pin 1 of the target connector) level. Level will be L if VTref is cut off.

\*2: Reference voltage needs to be input to VTref in order to detect the pulse.

Note that this function is available only in standalone mode.

The drive capability of the EX\_OK, EX\_NG, and EX\_BSY pins is as follows for both IOL/IOH.

| VTref      |      |

|------------|------|

| 1.65~1.95V | 4mA  |

| 2.3~2.7V   | 8mA  |

| 3.0~3.6V   | 24mA |

| 4.5~5.5V   | 32mA |

#### External input / output function using 3.3V I/F

This is provided because when power is supplied to the target system via FP-40, the VTref signal (target voltage) cannot be used as a reference power supply because power is turned on and off in synchronization with the FP-40 writing process.

Note that even when the FP-40 power supply function is not used, it can be used as a normal 3.3V external input/output signal.

However, the external I/O function powered by VTref (Pin 1) above and the 3.3V I/F external I/O function cannot be used together.

| Signal                    | Description                                         | Equivalent signal                                                                                                         |

|---------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| EX33_BSY                  | Outputs high from FP-40 during writing              | EX_BSY(3 pin)                                                                                                             |

| EX33_OK                   | When the write result is OK, H is output from FP-40 | EX_OK(17 pin)                                                                                                             |

| EX33_STARTn <sup>*1</sup> | Start writing when there is a pulse input to FP-40  | EX_STARTn(11 pin)                                                                                                         |

|                           | EX33_BSY<br>EX33_OK                                 | EX33_BSY     Outputs high from FP-40 during writing       EX33_OK     When the write result is OK, H is output from FP-40 |

\*1: Note that this function is available only in standalone mode.

#### The drive capacity of EX33\_BSY and EX33\_OK is as follows.

| Voltage |      |

|---------|------|

| 3.3 V   | 12mA |

#### EX\_OK/EX33\_OK

Three modes of output are available for EX\_OK. The presence or absence of the output and the mode switching of the output are performed in C-Flash (see below).

#### ① Result output (High at OK, Low at NG)

Hi is output when write completes successfully. If writing fails, nothing(L) is output.

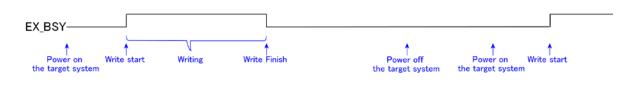

| ЕХ ОК                         |                  |         |              |                                    |                                 |             |

|-------------------------------|------------------|---------|--------------|------------------------------------|---------------------------------|-------------|

| Power on<br>the target system | ↓<br>Write start | Writing | Write Finish | ↑<br>Power off<br>the target syste | Power on<br>m the target syster | Write start |

#### 2 LED interlocking (Pulse output during writing, High at OK, Low at NG)

EX OK pulse will resemble the turning on and off of the STS LED on the FP.

The following waveform is output during Write operation and when the operation completes successfully:

| EX_OK                         |                  | ᠾ᠕         |              |                                |                               |                  |  |

|-------------------------------|------------------|------------|--------------|--------------------------------|-------------------------------|------------------|--|

| Power on<br>the target system | ↑<br>Write start | Writing *1 | Mrite Finish | Power off<br>the target system | Power on<br>the target system | ∱<br>Write start |  |

The following waveform is output during Write operation and when the Write operation fails:

| EX_OK                         |             |            |              |                                |                               |             |  |

|-------------------------------|-------------|------------|--------------|--------------------------------|-------------------------------|-------------|--|

| Power on<br>the target system | Write start | Writing *1 | Write Finish | Power off<br>the target system | Power on<br>the target system | Write start |  |

**\*1** : Low/Hi signal period may vary during Write operation

#### 3 Write interlocking (High during writing, Low after writing)

Hi is output on EX\_OK when Write operation is in progess. After write operation comepletes, irrespective of whether the Write operation succeeds or fails the signal level drops to L.

#### EX\_STARTn/EX33\_STARTn

EX\_STARTn starts writing when an external falling edge is detected on EX\_STARTn instead of the **PROGRAM switch**. To use this function, it must be set in C-Flash (see below).

Please note that edge detection of EX\_STARTn signal will be ignored when Write operation is in progress.

#### EX\_BSY/EX33\_BSY

To use EX\_BSY, it needs to be configured using C-Flash. (see below).

When EX\_BSY is configured, H is output during Write operation and L is output when Write operation completes. Please note that this signal is shared with the JTAG's TRST signal. Make sure not use this signal when the TRST signal of the CPU on the target system is connected to FP.

#### EX\_NG

To use EX\_NG, it needs to be configured using C-Flash. (see below) $_{\!\scriptscriptstyle \circ}$

When EX NG is configured, H is output when Write operation fails.

Please note that this signal is shared with the JTAG's TDI signal. Make sure not use this signal when the TDI signal of the CPU on the target system is connected to FP.

In External input/output function using 3.3V I/F, no signal is output.

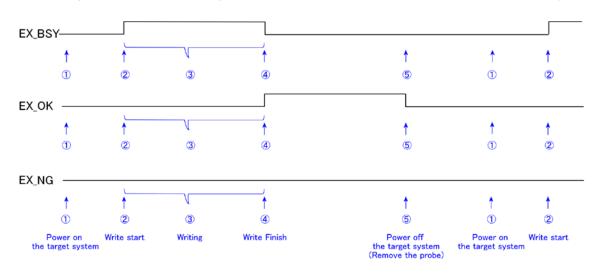

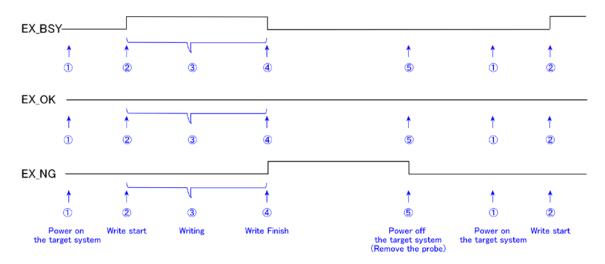

#### Using each signal in combination

By setting EX\_OK signal to "result output" and enabling the output of the EX\_BSY and EX\_NG signals, the three signals can be combined to determine the progress and result of Write operation with the external device. This also applies to EX33\_OK and EX33\_BSY signals of the External input/output function when 3.3V I / F is used. In External input/output function, EX\_NG signal is output using 3.3V I / F.

The following waveform is output during Write operation and when the operation completes successfully:

The following waveform is output during Write operation and when the Write operation fails:

H level will be the same as the VTref (Pin 1 of the target connector) level. The level will be L if Vtref is cut off. If VTref signal is interrupted, EX\_OK/EX\_NG signal will automatically output L. H will not be output even if VTref signal is restored after this during the current operation.

In External input/output function using 3.3V I/F, H level will be at 3.3V.

FP-40 monitors if External input/output function is powered by VTref (Pin 1) and if VTref signal is interrupted.

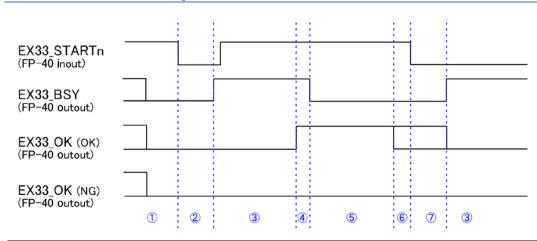

#### EX\_STARTn (FP-40 inout) ł ł VTref (Target Power) EX\_BSY (FP-40 outout) EX\_OK (OK) (FP-40 outout) EX\_OK (NG) (FP-40 outout) 1 2 4 6 0 8 9 10 3 :5: 1 FP-40 setup time(4500ms,Only immediately after the FP-40 power supply,Usually (1)) EX\_STARTn goes high after input of Vtref 2 Note that EX\_STARTn of FP-40 monitors the falling edge and does not recognize the rising edge. 3 HI retention of EX\_STARTn (no specified time) Write processing starts when the EX\_STARTn falling edge is detected. (5ms) 4 5 Processing before writing 6 Writing $\bigcirc$ EX\_BSY, EXOK change time 8 Result output(OK:EX\_OK/HI,NG:EX\_OK/LOW) 9 After FP-40 power down is detected, transition to next write occurs. 10 Waiting for the next start.

#### External I / O function timing with VTref (1 pin)

#### External I / O function timing with 3.3V I/F

| 1 | FP-40 setup time(4500ms,Only immediately after the FP-40 power supply)                                                                                                                            |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Write processing starts when EX33_STARTn falling edge is detected. (5ms)                                                                                                                          |

| 3 | Writing                                                                                                                                                                                           |

| 4 | EX_BSY, EXOK change time                                                                                                                                                                          |

| 5 | Result output(OK:EX_OK/HI,NG:EX_OK/LOW)                                                                                                                                                           |

| 6 | When the power supply function of FP-40 is not used,EX33_OK is LOW when there is no VTref input.<br>When the power supply function of FP-40 is used,EX33_OK keeps HI.<br>Wait time for next write |

| Ø | When the power supply function of FP-40 is used, EX_STARTn After recognizing the falling edge, set EX33_OK to LOW.                                                                                |

#### **C-Flash Settings**

Navigate to **[Target system setting] [Set Initial value]** tab. On clicking the **[External I/O Setting]** button, the following setting screen will be displayed:

|      | Setting of external input / output                                                                                                                                                | ×                                                                                                                                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]— | Power supply selection     Not use     External I/O powered by VTref (1 pin)     C Ex                                                                                             | ternal I/O with 3.3V I/F                                                                                                                                                                                     |

| [2]— | External I/O function powered by VTref (1 pin) Use Start writing input signal(EX_STARTn/11pin) C Disable © Enable                                                                 | External input / output with 3.3V I/F<br>Use Start writing input signal(EX33_STARTn/19pin)<br>© Disable<br>C Enable                                                                                          |

| [3]— | External OK output signal(EX_OK/17pin)     O Disable     C Enable(High at OK, Low at NG)     C Enable(High at OK, Low at NG)     C Enable(High during writing, Low after writing) | External OK output signal(EX33_OK/18pin)<br>© Disable<br>© Enable(High at OK, Low at NG)<br>© Enable(Pulse output during writing, High at OK, Low at NG)<br>© Enable(High during writing, Low after writing) |

| [4]— | External NG output signal(EX_NG/5pin)     O Disable     Enable(High at NG, Low at OK)                                                                                             |                                                                                                                                                                                                              |

| [5]— | C External BSY output signal(EX_BSY/3pin)<br>C Disable<br>C Enable                                                                                                                | External BSY output signal(EX33_BSY/16pin)<br>© Disable<br>© Enable                                                                                                                                          |

|      | OK Cancel                                                                                                                                                                         |                                                                                                                                                                                                              |

#### [1] Power supply selection

Select whether to use VTref or 3.3V I/F. Both cannot be used simultaneously. When **[Do not use]** is selected, each signal is automatically set to [Do not use/output].

#### [2] Use Start writing input signal

Input signal to FP-40 to start the Write procedure. [Enable] is automatically selected if the power supply is set to enable in the power supply selection.

#### [3] External OK output signal

Select the output format of the OK signal.

#### [4] External NG output signal

Selects the output of the NG signal. Note that the 3.3V I/F does not provide a signal equivalent to EX\_NG. **[Enable]** is automatically selected if the power supply is set to enable in the power supply selection.

#### [5] External BSY output signal

Select the output format of the BSY signal.

[Enable] is automatically selected if the power supply is set to enable in the power supply selection.

Press the **[Write]** button to reflect these setting in FP-40 (Otherwise, these settings will not be reflected in Standalone-mode).

If **[Write]** is grayed out and can not be pressed, refer to "4.3 Target System Settings" and "3.2.2 Specifying the data (file) for writing into on-chip flash memory" in "Onboard Flash Memory Programmer FP User's Manual"to make various settings of C-Flash until the **[Write]** button becomes enabled. Press the **[Write]** button.

| C-0          | Flash        | for F               | P-E           |              |              |               |              |                |              |  |

|--------------|--------------|---------------------|---------------|--------------|--------------|---------------|--------------|----------------|--------------|--|

| <u>F</u> ile | <u>E</u> dit | $\underline{V} iew$ | <u>S</u> et   | <u>T</u> ool | <u>D</u> ata | System        | <u>W</u> in  | dow <u>I</u>   | <u>H</u> elp |  |

| 🗃<br>Load    | 🦻<br>Reloa   | d   Ta<br>d   Se    | rset<br>tting | ്<br>Init.   | Read         | <b>W</b> rite | Erase<br>All | Erase<br>check | SUM          |  |

|              |              |                     |               |              |              |               |              |                |              |  |

|              |              |                     |               |              |              |               |              |                |              |  |

|              |              |                     |               | 0120         |              |               |              |                |              |  |

| Ready        | -4           | Flash               | mode (        | Withou       | t the tar    | get conne     | ection,      | ,              |              |  |

#### Done.

#### Note

The external I/O settings are saved in the C-Flash project file. If C-Flash is launched with a project file in which external I/O functions are disabled, and if a **[Write]** is performed on FP-40 on which external I/O functions are enabled, the external I/O function will be disabled according to the settings in the project file.

### Power supply

FP-40 has the ability to supply 3.3V or 5.0V power to the target system up to 200mA (simultaneous use of 3.3V and 5.0V power supplies is not possible.) An example using X3.3V power supply is shown below.

#### **C-Flash settings**

The signal output settings are made in the [Power Supply/External Signal] tab of the [Target Settings] in C-Flash. For details, please refer to the "CM1002\_On-board\_Flash\_Programmer\_FP\_Users\_Manual".

# **CPU-specific supplement**

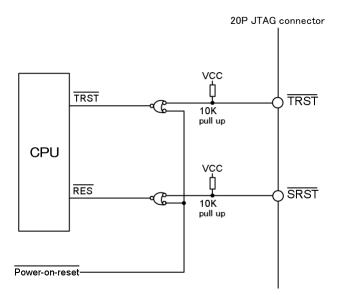

### Reference : RZ/A and RZ/T series /SRST, /TRST reference diagram

It may be required to control the  $\overline{\text{RES}}$  and  $\overline{\text{TRST}}$  CPU pins so that they are in low state at power on. Refer the CPU datasheet for details.

### STM32C031C6T6/UART

When using UART with STM32C031C6T6, connect the following signals:

| CPU      |    |              | FP            |     |  |

|----------|----|--------------|---------------|-----|--|

| Name No. |    | Function     | Name          | No. |  |

| PA10     | 33 | RX(INPUT)    | TXD(OUTPUT)   | 9   |  |

| PA9      | 21 | TX(OUTPUT)   | RXD(INPUT)    | 7   |  |

| PF2-NRST | 10 | Reset(INPUT) | SRSTn(OUTPUT) | 15  |  |

In addition, you will need to connect GND and VTref (one pin on the FP side).

•For information about the CPU side signals, be sure to refer to the CPU manual.

•For information about the pin numbers for the FP side signals, please refer to "Target interface specifications when using UART on the FP-40 unit".

#### Note

- To prevent malfunction, the length of wirings from the CPU to the target connector should be kept as short as possible.

- If the waveform disturbance exceeds the device specifications, suppress the disturbance by inserting a damping resistor into the signal line or use other means.

#### Technical Information on On-board Flash Programmer FP-40 (Eighth Edition)

Go through the required procedures as stated under Foreign Exchange and Foreign Trade Control Law in exporting (including the case where travellers directly carry) this product or providing this product for residents outside Japan.

- > No part of this manual, whether in whole or in part, may be adapted, copied or reproduced without prior permission.

- > The content of and the specifications of this product are subject to change without prior notice.

- Computex Co., Ltd. shall not be held liable for any loss or damage arising from the use of this product although all possible measures have been taken by Computex Co., Ltd. in good faith to ensure the quality of the product.

- Contact us for any questions, feedback, comments, requests or anything of concern to you (or in the event of malfunction) regarding this product or misprinting or missing information within this manual.

- > Other names of CPUs etc. mentioned in this manual are trademarks or registered trademarks of their respective manufacturers.

- > COMPUTEX is registered trademark of Computex Co., Ltd. in Japan.